Two electronic chip manufacturing units, which entail a combined investment of Rs 51,550 crore and would enjoy government subsidy, are likely to be operational in the country in the next two years.

Two electronic chip manufacturing units, which entail a combined investment of Rs 51,550 crore and would enjoy government subsidy, are likely to be operational in the country in the next two years.

Two consortia– one led by Jaiprakash Associates in association with IBM and the other led Hindustan Semiconductor– have proposed setting up these plants.

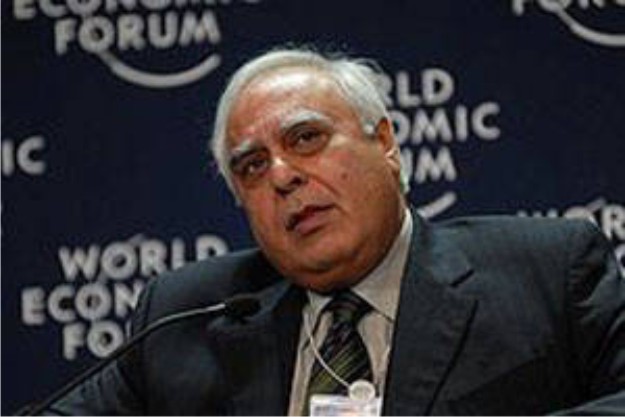

Communications and IT Minister Kapil Sibal said setting up of electronic chip facilities will also be of nation’s strategic purpose as chips have security implications.

“There are strategic sectors like atomic energy sector, space, defence and power. In all of these you need chips. There are security considerations. It will serve our strategic purpose. There are security consideration. The fabs should be operational in about two years from now,” Sibal said here.

At present there is no electronic chip manufacturing or semiconductor wafer fabrication plant in India. Over 90 per cent of the domestic electronic requirement is met through imports.

Government will also hold 11 per cent stake in each project, while technology providers are required to hold 10 per cent stake holding.

Department of Electronics and Information Technology Secretary J Satyanarayana said: “One plant is proposed by a consortium led by Jaiprakash Associates, along with IBM Microelectronics and the system integrator is Tower Jazz. The outlay of the proposed fab is about Rs 26,300 crore.”

This unit is likely to come up in Greater Noida in UP. “The other plant is from Hindustan Semiconductor Manufacturing Corporation (HSMC) along with France-based ST Microelectronics and Silterra (Malaysia). The outlay of this proposed fab is about Rs 25,250 crore,” Satyanarayana said.

The proposed location of this plant is in Gujarat. Government is yet to work out the details of subsidy the proposed projects will enjoy. Subsidy will depend on detailed project report to be submitted by the two consortia.

Sibal said that the about 60 per cent of incentives approved by Cabinet are already covered under existing policies. In addition to this, the Finance Ministry has agreed to give them status under section 35 AD of I-T Act which means capital investment amount will be set off against profit.

“They will be given interest free loan. This along with recognition under 35 AD will constitute balance 40 per cent of incentives to be provided to them,” Sibal said.

Also, the loan amount given to the companies will be converted into 11 per cent equity in these projects, Satyanarayana said. Sibal said that electronic chip manufacturing is highly capital intensive business and long gestation period.

“No body was interested in setting up wafer fab here unless you give them large concessions. It is zero duty in any country. We had to attract investors,” he said. Out of total 16 interest received by government, only the two consortium showed seriousness, the minister said.